# 耐放射線FPGA(Field Programmable Gate Array)

岡山大学 学術研究院環境生命自然科学学域(工) 教授 渡邊 実

2024年7月23日

#### 研究背景

- □ 想定される用途

- 福島第一原子力発電所の廃炉作業ロボット・システム

- 原子力発電所の各システム

- 核融合炉のシステム(未来)

- 宇宙システム

- 放射線医療システム

- □ 問題点(福島第一原子力発電所の廃炉現場について)

- 福島第一原子力発電所デブリ付近は1,000 Sv/hもの放射線環境

- 集積回路のトータルドーズ耐性が圧倒的に不足

- 廃炉作業に使用できる集積回路が無い

- 原始的な(エアバルブ、電力駆動)ロボットしか使えない

|                                   | ASIC<br>RAD750<br>(0.15um) | Anti-Fuse<br>FPGA<br>RTAX4000D<br>(0.15um) | Flash<br>FPGA<br>RT4G150<br>(65nm) | SRAM-<br>FPGA<br>XQR5VFX130<br>(65nm) |

|-----------------------------------|----------------------------|--------------------------------------------|------------------------------------|---------------------------------------|

| Total-Ionizing-<br>dose Tolerance | 2 Mrad                     | 300 krad                                   | 160 krad                           | 2 Mrad                                |

| Life Time at 1,000 Sv/h           | 20 hr.                     | 3 hr.                                      | 1.6 hr.                            | 20 hr.                                |

2

#### 目的

- □ 集積回路が使用できれば

- 2足歩行ロボット、最先端ロボットの投入が可能になる

- □ 現在の解決策

- ・ シールド(鉛、タングステン等)

- MEMS, SiC等の耐放射線デバイスの研究があるが集積度に難がある

- 既存の集積回路の放射線耐性を高めることは??

- □ 修理可能なVLSIを提案

1

#### 修理可能なVLSIとは?

条件:構成回路だけは壊れてはならない

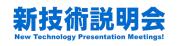

#### 既存のプログラマブルデバイス (FPGA)

## FPGAの構成回路(プログラミングを支援する回路) は放射線に対して極端に脆弱である

シリアル方式の構成回路では1か所でも故障があると全体の構成 (プログラミング)が不可能になる。

#### 既存のFPGA構成回路の生存確率

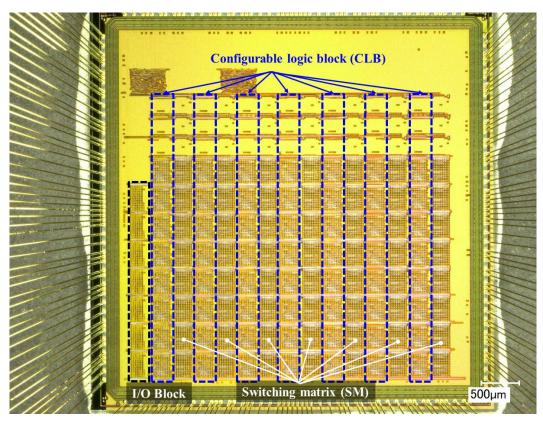

当研究室で設計されたFPGA

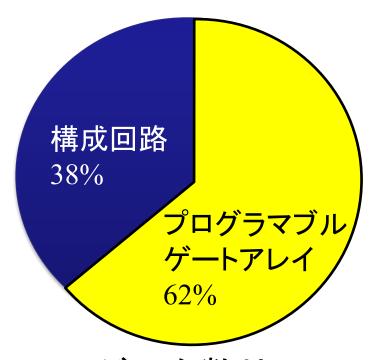

既存のFPGAでは構成回路はチップ面積の38%以上を占める

トランジスタ数比

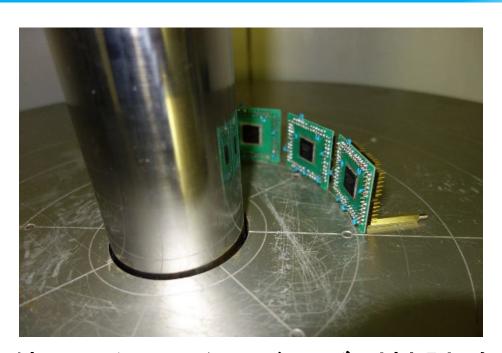

#### Cyclone II FPGAの耐放射線試験

Co60を使用したトータルドーズ耐性試験の様子

- □ Cyclone II FPGA)に対してトータルドーズ耐性試験を実施

- □ 35~65 kradのTIDで全てのFPGAが破壊された

- □ このすべてにおいて最初に構成回路が破壊されていることを確認

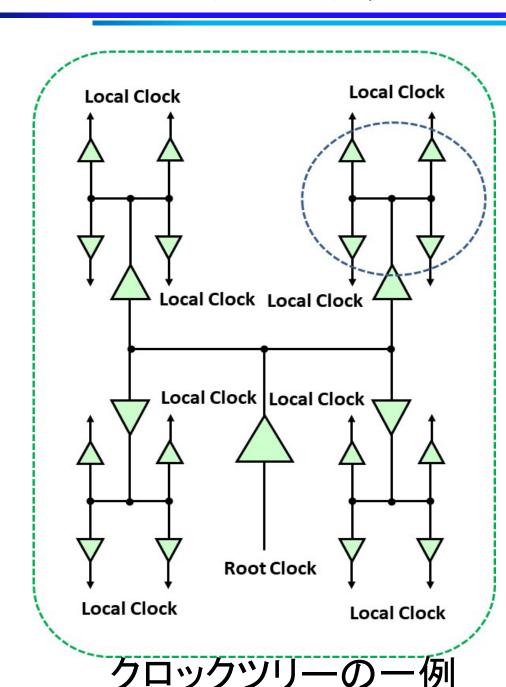

#### クロック分配における問題点

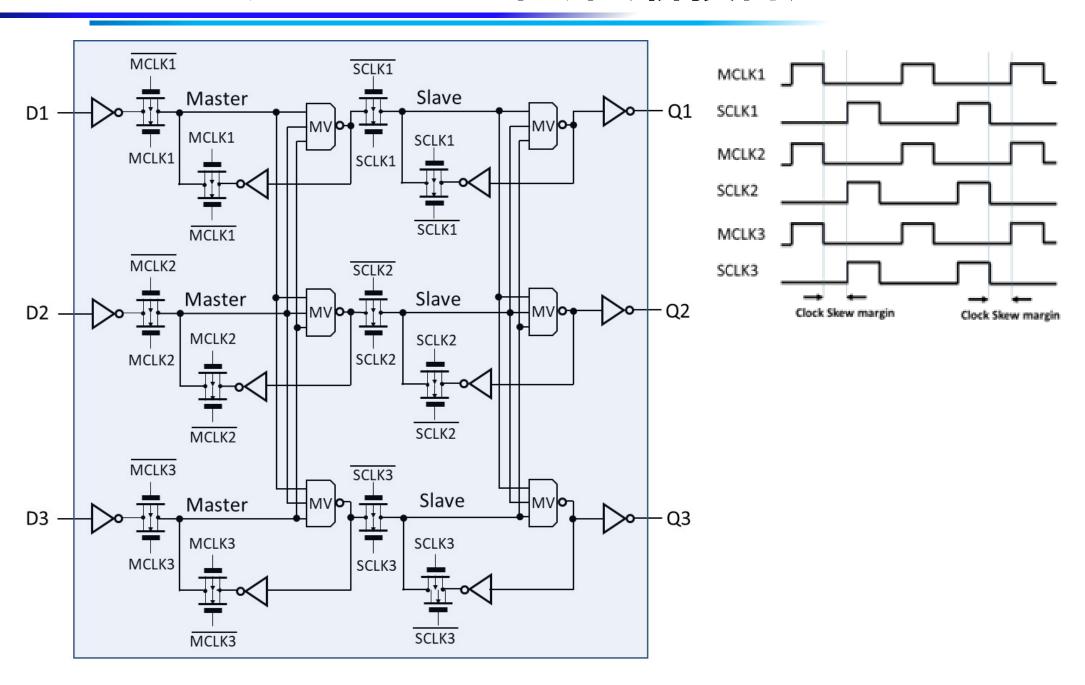

放射線環境下ではクロックスキューが増大する

FPGAの構成回路に使用されるシ フトレジスタ回路は最もクロックスキューマージンの少ない回路

#### 修理可能なVLSIの実現のために

- ロトランジスタ故障への対策

- ✓ 構成回路の冗長化が必要

- ✓ 3重化構成回路の導入

- ロクロックスキュー増への対策

- ✓ 2相クロックの導入

上記を実現する 「耐放射線FPGA」 の提案

9

#### フリップフロップ回路(新技術)

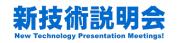

#### 3重化論理ブロック

- □3重構成回路

- □3重論理ブロック構造

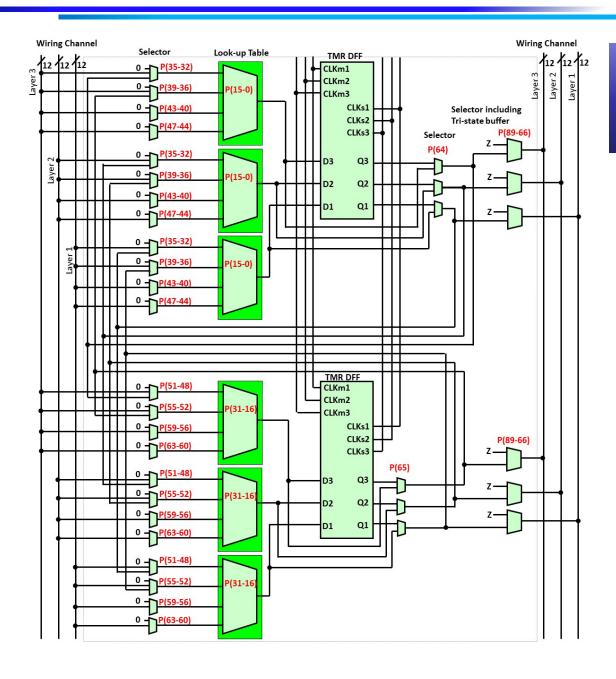

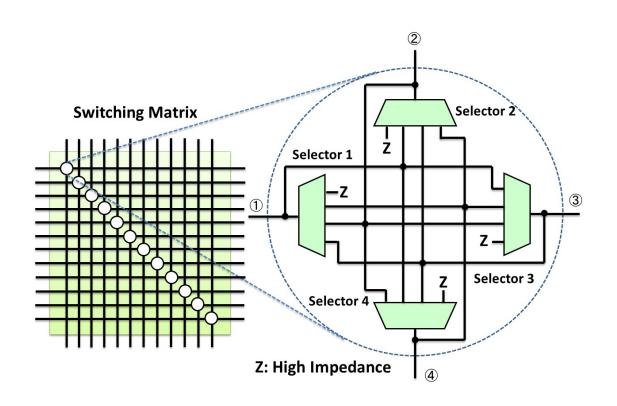

#### 3重化スイッチングマトリックス

□ 3重構成回路□ 3重スイッチングマトリックス構造

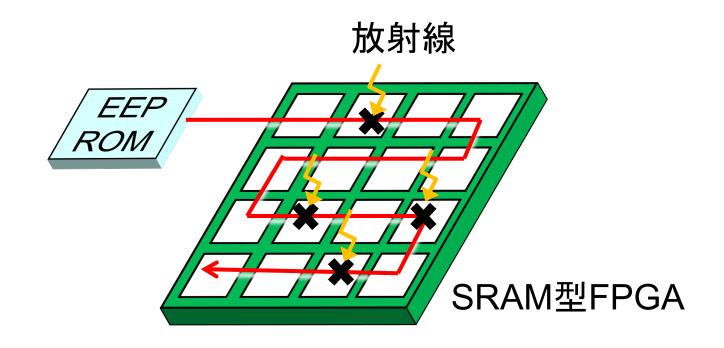

#### 新FPGAチップの仕様

チップ写真

| Process Tech                | 0.18 µm<br>Standard CMOS<br>process |                                                                                          |  |  |  |

|-----------------------------|-------------------------------------|------------------------------------------------------------------------------------------|--|--|--|

| Metal Layer                 | 5 Metal Layers                      |                                                                                          |  |  |  |

| Die Size                    | $5 \text{ mm} \times 5 \text{ mm}$  |                                                                                          |  |  |  |

| Supply Voltage              | Core: 1.8 V, I/O: 3.3 V             |                                                                                          |  |  |  |

| Gate Array<br>Construction  | CLB                                 | 70 cells × 3 Layers Each cell includes two 4-input Look- Up Tables and two D flip-flops. |  |  |  |

|                             | SM                                  | 77 cells × 3<br>Layers                                                                   |  |  |  |

|                             | IOB                                 | 7 cells (I/O: 28 bits) × 3 Layers                                                        |  |  |  |

|                             | Wiring Channel                      | 12 wires                                                                                 |  |  |  |

| Gate Count                  | 2,380 gates × 3<br>Layers           |                                                                                          |  |  |  |

| Number of C                 | 92 bits                             |                                                                                          |  |  |  |

| Configurat S                |                                     | 96 bits                                                                                  |  |  |  |

|                             | OB                                  | 64 bits                                                                                  |  |  |  |

|                             | otal                                | 14,280 bits                                                                              |  |  |  |

| Total-lonizing<br>Tolerance | 7.3 MGy (Co60)<br>6.6-6.7 kGy/h     |                                                                                          |  |  |  |

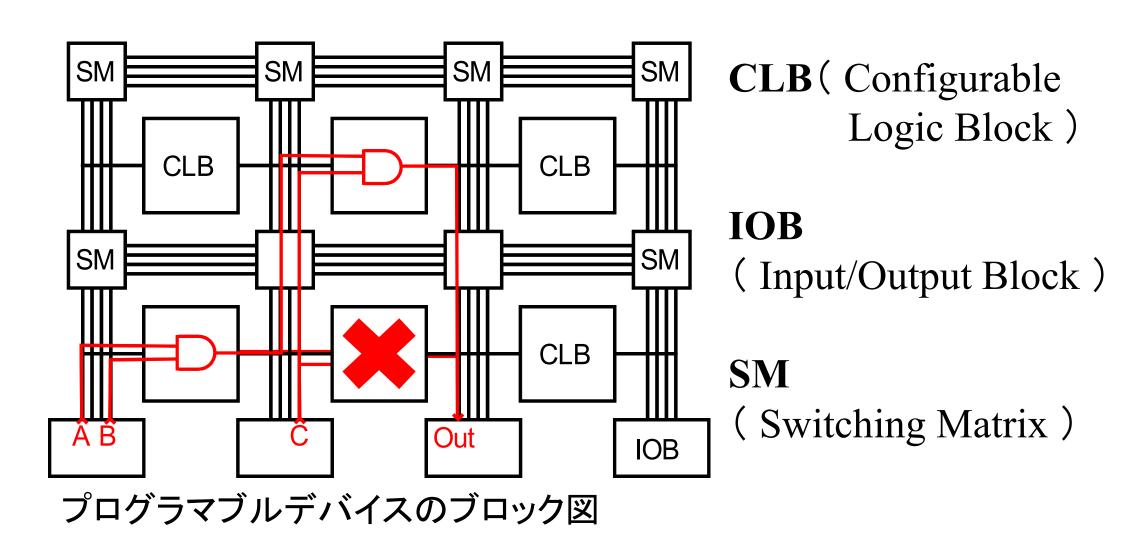

#### ソフトエラー

- ロソフトエラー

- 放射線が集積回路に入射すると、メモリの値、フリップフロップの値などが反転する現象が生じる

- □ 恒久故障ではないので正しい情報を再度書き込めば復旧できる

- ロ ソフトエラー対策

- □ 3重回路実装(TMR)

- ロ スクラビング(メモリへの対策)

- □ メモリのデータを読み出しては訂正して書き戻すという処理をサイクリックに行うこと

- □ FPGAの場合には構成メモリで必須となる

| TMR周期 | 100 ms    | 1 ms      | 10 μs     | 10 ns     |

|-------|-----------|-----------|-----------|-----------|

| MTBF  | 31.7 sec. | 50.0 min. | 3.47 days | 9.5 years |

#### 既存のFPGAのソフトエラー耐性

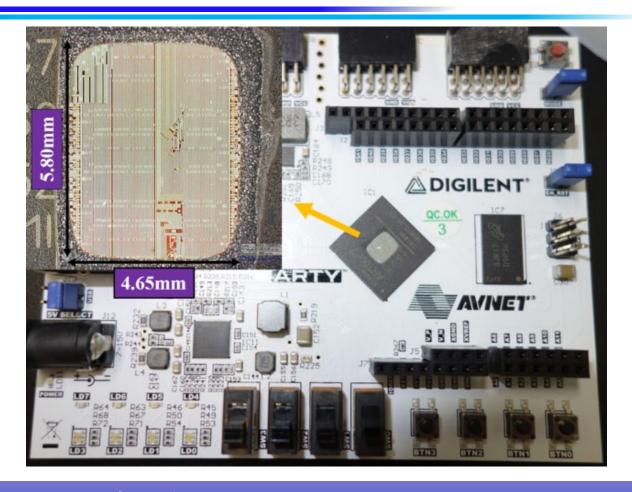

Am241(4 MBq)のα線源を用いたArtix-7 (XILINX FPGA)による構成試験の 様子

- □ チップトップは開封、チップ直上にAm241を設置

- □ 構成は1度たりとも成功せず

#### 新FPGAのソフトエラー耐性

Am241(4 MBq)のα線源を用いた新FPGAのソフトエラー耐性試験を実施チップ直上にAm241を置いた状態

□1時間、連続構成試験を行い1回たりとも構成に失敗せず

#### まとめ

#### 新技術(フリップフロップ)

- □トータルドーズ効果により故障が生じる問題

- ✓ 故障するトランジスタの問題

- 3重化構成回路で解決

- ✓ クロックスキューが増大する問題

- 2相クロックで解決

- 新FPGAの開発に成功

- ✓ 7.3 MGyのトータルドーズ耐性を実現

- 福島第一原子力発電所(1000Sv/h)で300日使用可能

- ✓ 高いソフトエラー耐性も実現

- 4MBqのAm241にてエラーゼロ

#### 実用化に向けた課題

- チップ量産

- スタンダードなCMOSプロセスにて量産可能

- 量産についての障害は無い

- ツールの開発

- FPGAの開発ツールが未整備である

#### 本技術に関する知的財産権

• 発明の名称 :集積回路

• 出願番号 : 特願2023-125483

• 出願人 : 岡山大学

● 発明者 : 渡邊 実

### お問い合わせ先

## 岡山大学 研究・イノベーション共創機構 知的財産本部

Tel: 086 - 251 - 8417

e-mail: chizai@okayama-u.ac.jp

URL: https://www.orsd.okayama-u.ac.jp